先进技术

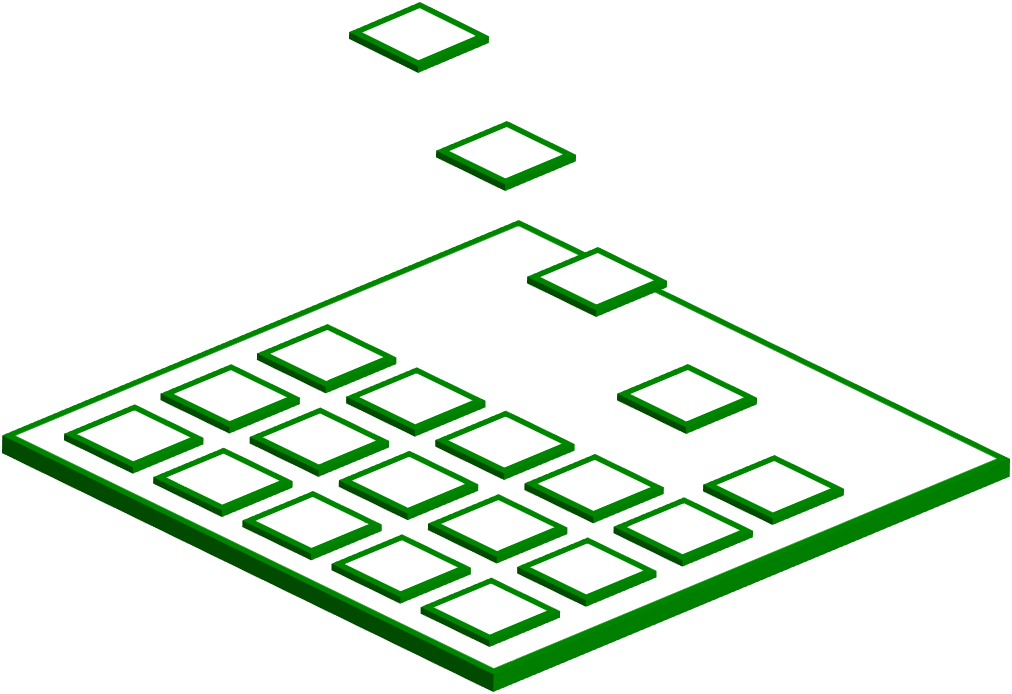

面板级扇出技术

扇出封装将成为高阶组件应用的主流,特别是多芯片整合,主动式与被动式组件的异质整合。面板级扇出封装可实现高密度互连、优异的电性和功耗表现。与晶圆级扇出相比,力成的面板级扇出封装具有利用率和单位产量高的生产效率优点。

面板级扇出方案

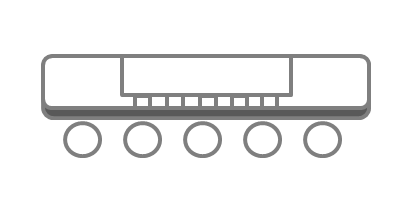

CHIEFS®

Chip First

- 较CLIP®具成本优势

- 应用处理器芯片、基频芯片、特殊应用芯片、电源管理芯片、内存芯片

- 支持多芯片封装 (双芯片/ 三芯片)

- 芯片背面外露

- 最小重布线路线宽/线距大于等于 5/5um

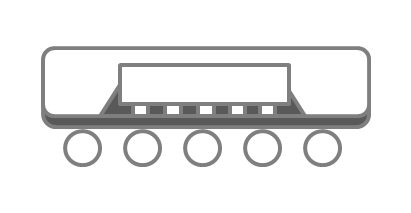

CLIP®

Chip Last

- 已知良好重布线路层(RDL),避免芯片损失

- 被动组件之嵌入式整合

- 中央处理器、图像处理器、现场可程序化逻辑门阵列芯片、热敏组件

- 支持多芯片封装 (可多于三芯片)

- 最小重布线路线宽/线距大于等于 5/5um

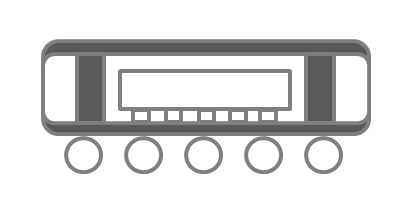

PiFO®

Chip Middle

- 双面重布线路结构, 电镀铜柱作为上下层重布线路之互连

- 支持被动组件整合

- 射频模块、传感器、应用处理器芯片、光学组件、系统级封装…等3D堆栈之应用

- 靠近芯片背面之最小重布线路线宽/ 线距大于等于 5/5um,靠近芯片正面之最小重布线路线宽/线距大于等于 2/2um

BF2O®

Bump Free

- 毋需晶圆凸块制程

- 适用于I/O数少,层数需求低与单颗芯片之封装

- 电源管理芯片、音频芯片、功率放大器

- 最小重布线路线宽/线距大于等于 15/15um

优异性能与创新技术

- 与晶圆级扇出封装相比,面板级扇出封装提供更高的生产效率

- 提供四种封装结构,包括Bump-free, Chip First, Chip Last 及 Chip Middle

- 多组件异质整合封装,包括主动组件与被动组件

- 提供细间距与高铜柱,实现垂直组件整合

- 透过精细的重布线层(线宽/线距)提供高密度互连

- 低温固化的介电材料以满足逻辑和内存多样的组件需求

- 卓越的设计、制程与故障分析工程能力,提供坚固耐用的封装

- 优异的热、机械与电性模拟能力,为客户提供最佳封装设计和用料清单

- 可提供面板级扇出封装成品之一站式服务与嵌入芯片之扇出重布线路基板

应用

- 兼容于逻辑与内存组件并涵盖支持低 I/O 到高阶产品需求

- 应用广泛,包括电源、射频、消费性电子产品、行动装置、储存设备、汽车、高效能运算、天线封装等

技术特点

- 提供系统级封装 (SiP),允许多芯片与被动组件整合

- 透过精细的重布线线宽与线距及最短的讯号传输路径,提供良好的电性效能

- 细间距电镀高铜柱,运用于多样的扇出型堆栈封装需求