先進技術

晶圓凸塊

晶圓凸塊是在晶圓上形成的金屬凸塊,每個凸塊都是一個積體電路信號接點。有別於傳統的打線接合,打線接墊是位於周邊區域,而凸塊的輸入輸出接墊則可分佈於晶片的所有表面,因此可縮小晶片尺寸並最佳化電性路徑。隨著小型化與高效能封裝的發展,凸塊封裝逐漸取代傳統的打線封裝。

凸塊

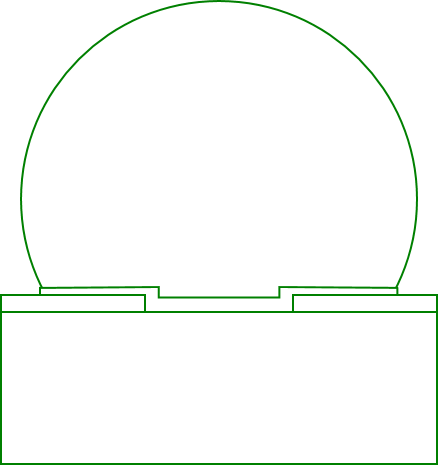

焊料凸塊

隨著元件數量的不斷增加,凸塊正在取代打線作為連接方法。在所有凸塊類型中,無鉛凸塊在覆晶技術中的生產歷史最為悠久。無鉛凸塊是在半導體元件的接觸墊上形成的球狀焊料,隨後用於覆晶接合。力成自2013年起開始量產。

能力

- 凸點間距 130~250 微米

- 凸塊高度 70~100 微米

- 可選用聚酰亞胺(PI)層用於邏輯和記憶體元件

Bumping

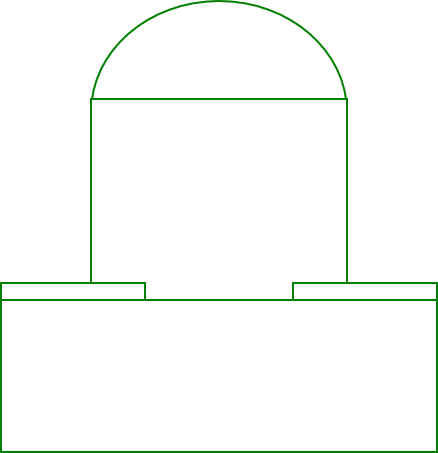

銅柱凸塊

銅柱凸塊(CPB)結構具有更佳的抗電子遷移能力、降低功率損耗及訊號延遲,以及更佳的散熱效能。與焊料凸塊相比,銅柱凸塊技術還能有效地控制接點直徑和突出高度,從而形成細間距接點。可應用於行動應用處理器、高效能運算、基頻、記憶體、特殊應用晶片和系統單晶片。自 2013 年起,PTI 擁有生產經驗,包括各種邏輯和記憶體裝置。

能力

- 凸塊間距 40~130 微米

- 最大凸塊高度 103 微米

- 可選用聚酰亞胺(PI)層用於邏輯和記憶體元件

Bumping

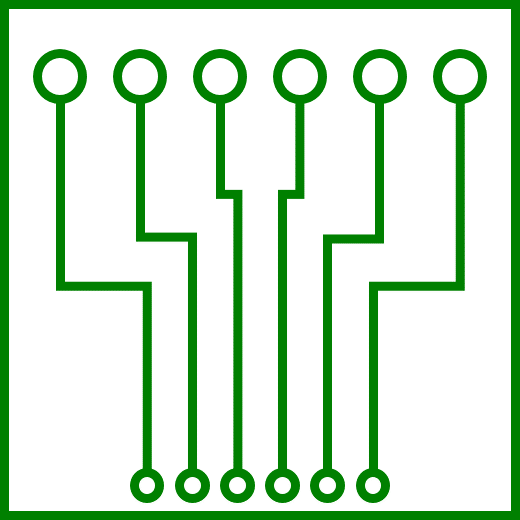

重佈線層解決方案

銅鎳金重佈線層主要應用於需要高耐蝕性、高可靠性、良好焊接性的封裝技術,因為Au表面能減少氧化並提供低損耗的訊號傳輸。銅重布線則主要應用於高密度、高效能、低成本的先進封裝,提升 I/O 密度並減少封裝尺寸。

能力

- 銅與銅/鎳/金之重佈線層

- 最小線寬/線距為 5微米/5微米

- 結構:2P1M、2P2M和3P2M